原理

-

右図は PLL 検波の原理図です。

右図は PLL 検波の原理図です。

-

PLL 検波はフィードバック系を持ちます。

-

FM 入力には IF 周波数の 10.7MHz が使われます。

-

VCO というのは電圧制御型発振回路のことで、10.7MHz 近辺の周波数で発振しています。

-

位相比較器というのは FM 入力周波数と VCO 発振周波数を比較して、そのズレの比較結果を±の電圧値で出力します。

-

LPF というのはローパスフィルターです。

-

周波数変調された FM 入力と VCO の周波数は常に位相比較されており、その比較結果は LPF を経て VCO に帰還されます。

この結果、VCO の周波数が常に FM 入力の周波数と一致するように制御されます。

その制御出力の電圧の変化が検波出力になります。

-

PLL 検波はこのように原理が簡単なので特殊な部品も必要なく、簡単でコストが安く高性能な検波回路を構成しやすいです。

また、「リミッタを用いないスレショルド改善が可能」というメリットもあります。

-

PLL 検波にも欠点があります。

-

それは電圧−周波数変換に使われるバリキャップダイオードの直線性が悪いと検波の直線性も悪くなることです。

-

欠点の解決方法について

-

まずは直線性に優れたバリキャップダイオードを使う。

-

更に直線性補正回路を制御ループ内に組み込む。

KENWOOD / TRiO でいう DLLD 回路がこれに相当します。

バリキャップ制御は直流(低周波)ですから、周波数が低いので補正は比較的やりやすいです。

一般的な PLL 検波回路

-

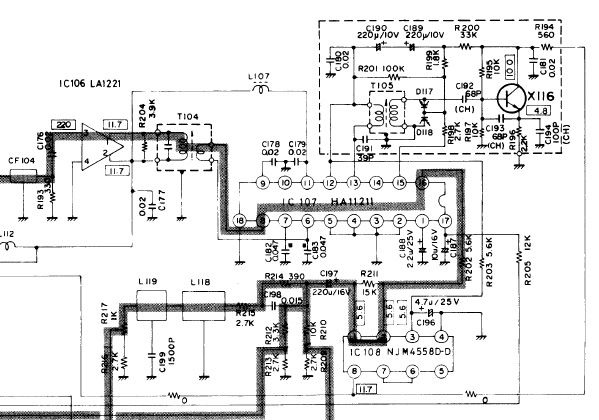

回路図は

SONY ST-S555ESX

の PLL 検波部分です。

回路図をクリックすると元の pdf ファイルが見られます。

回路図は

SONY ST-S555ESX

の PLL 検波部分です。

回路図をクリックすると元の pdf ファイルが見られます。

-

「D204 と D205 でバランスド検波をして位相検出→Q208 によるコルピッツ発信器にフィードバック」となっています。

-

IF 周波数の変化に対して電圧フィードバックをかけて発信器を同期化します。

-

このフィードバック電圧=検波出力となります。

-

この回路構成が PLL 検波では一般的です。

Victor のちょっと変わった PLL 検波回路

・・・ 参考文献は

こちら

です。

-

Victor T-7070

や

Victor T-2020

ではちょっと変わった PLL 検波回路になっています。

Victor FX-711

では一般的な PLL 検波回路なので、Victor の古典的 PLL 検波回路 (ここでは Victor 式 PLL 検波回路 と呼びます。) と思います。

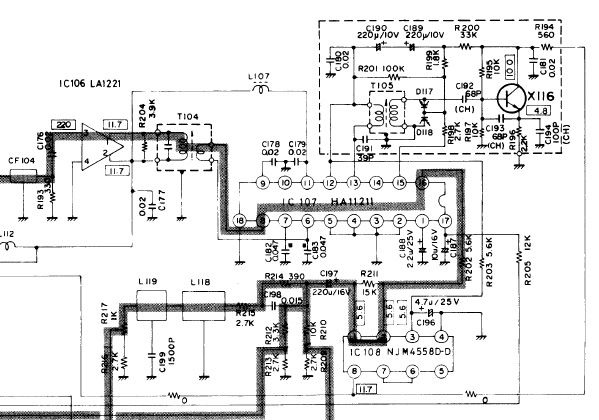

右の回路図は T-7070 の PLL 検波回路です。

Victor T-7070

や

Victor T-2020

ではちょっと変わった PLL 検波回路になっています。

Victor FX-711

では一般的な PLL 検波回路なので、Victor の古典的 PLL 検波回路 (ここでは Victor 式 PLL 検波回路 と呼びます。) と思います。

右の回路図は T-7070 の PLL 検波回路です。

-

Victor 式 PLL 検波は [

HA11211

]+[ディスクリート回路] で構成します。

-

[HA11211] ですから、基本はクォードラチュア検波です。

通常のクォードラチュア検波では以下の構成になります。

-

[HA11211] 14pin から出力される [リファレンス IF 周波数] と同相の周波数をコイルを介して [HA11211] 13pin に注入します。

-

[HA11211] 12〜13pin に90度位相シフトの目的で、広帯域同調コイル(Q が低い)を接続します。

-

Victor 式 PLL 検波では [HA11211] 12〜13pin に 10.7MHz 近辺の VCO 出力を接続します。

-

VCO を制御するのは [HA11211] 15pin の AFC 出力です。

-

AFC 出力とは [リファレンス IF 周波数] と [VCO 出力周波数] を位相比較した結果を電圧値で示す出力です。

[HA11211] 12pin のラインがクォードラチュア検波のイマジナルグランドです。

-

[VCO 出力周波数] が [リファレンス IF 周波数] を 90度位相シフトした周波数に合致するとこのイマジナルグランドを基点として 0V になり、位相が進遅に対して+−に振れます。

-

VCO を制御するのがこの AFC 出力ということは、IF 周波数の変化に VCO が追随し、広い範囲で90度位相シフトを正確に行えることを意味します。

-

C189, C190, R199, R201 が PLL 回路のループフィルタになります。

-

通常のクォードラチュア検波では同調コイルの経年変化や温度変化で位相がズレやすいですが、Victor 式 PLL 検波では AFC を使ったフィードバック系でこのズレを吸収できるメリットがあります。

-

通常のクォードラチュア検波では正しく90度位相シフトされているのは中心周波数 10.7MHz だけで、この中心周波数から離れるごとに少しずつ位相がズレます。

これがクォードラチュア検波の歪率悪化と S/N 悪化につながります。

Victor 式 PLL 検波では広帯域で正しく90度位相シフトされるようフィードバック制御され、歪率と S/N の優位性があります。

-

結論として、

Victor 式 PLL 検波は改良型クォードラチュア検波

と言えます。

右図は PLL 検波の原理図です。

右図は PLL 検波の原理図です。